[Ushiba, YamaT]

Abstract

- This post is related to the glitch issues on ITMX F3_GAS (klog#20639) and ITMY ACC_H2 (klog#20636)

- Glitch issue was solved by replacing ADC board, ADC adapter board, and ADC internal cable.

- After replacing ADC, timing error occurred on both K1IX1 and K1IY1.

- We can do the local measurements on ITMX and ITMY.

- But measurements with channels on ITMX/ITMY and other RTFEs were affected by this issue.

Details

For DGS experts

In order to investigate glitch issues, we replaced ADC board, ADC adapter board and ADC internal cable.

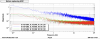

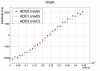

Glitches vanished and noise level was improved by this replacement.

However, timing error cannot be fixed after ADC replacement.

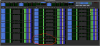

Now ADC DT on k1iopix1 and k1iopiy1 are "20" [us] (See Fig.1).

This means that timing on ADC delayed as 1-sample on 64kHz (nominal ADC DT is "5" [us])

And also, according to the IRIG-B channel, timing delayed form nominal timing as 4-5us.

(Current value is 7 and nominal is 11 or 12.)

This issue seems to be different from "IRIG-B 999997" problem (e.g. klog#583 and klog#6031).

Maybe 4-5us delay is rounded up to the integer multiples of 1/65536Hz.

In fact, timing duotone signal delayed as 1-sample only on k1iopix1 and k1iopiy1.

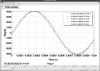

Fig.2 shows the duotone ADC signal on some RTFEs.

On k1lsc0 and RTFEs for ETMs, signals across to 0 between the first and the second sample points counted from integer GPS time.

On the other hand, signals across to 0 between the second and the third sample points counted from integer GPS time.

I'm now doubting the difference of the product lot of ADC.

ADCs that we installed today were purchased in FY2021 (S2113340 for IX and S2113341 for IY).

From the view point of noise, we need to replace ADC card form original ones.

We need to solve this problem before starting global control.